Citrobits launch the HyperRAM™ Reference Design for imaging and video processing applications

Citrobits announced the release of its new HyperRAM™ Reference Design, a high-performance, power-efficient solution tailored for memory-intensive embedded applications. Built on the award-winning Lattice Nexus™ FPGA platform, the reference design is optimized for tasks such as sensor fusion, frame buffering, overlays, and advanced imaging and video processing.

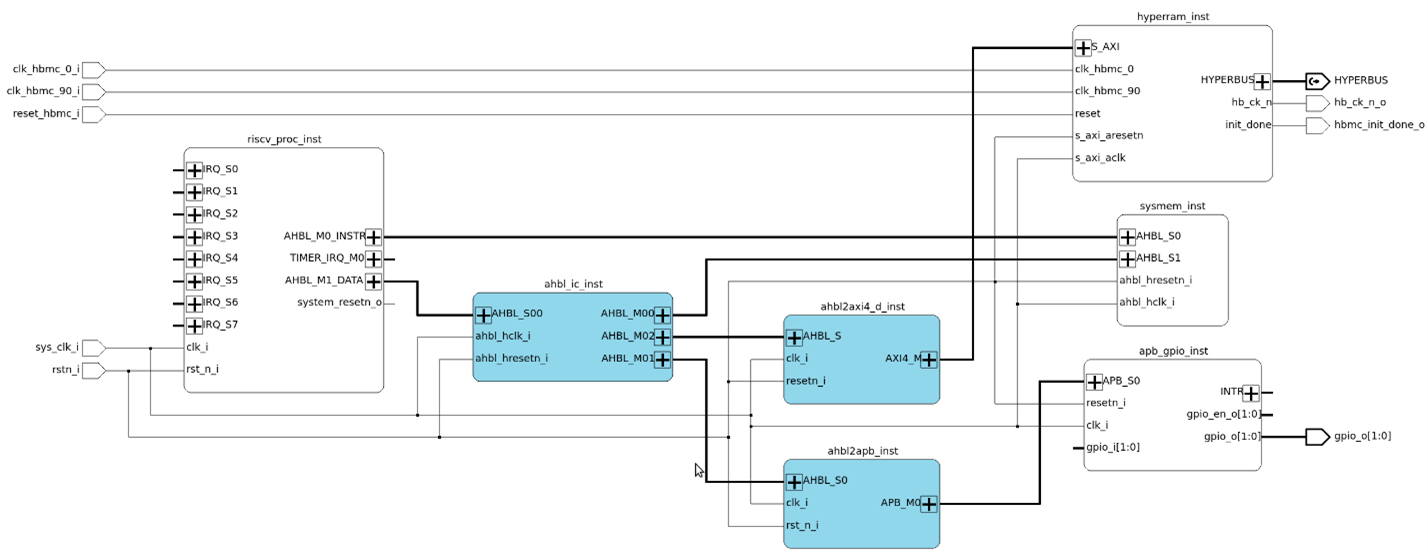

This high-performance reference design features the Citrobits HyperBus™ Controller, operating at speeds up to 200 MHz and utilizing the industry-standard AXI4 interface for seamless integration into modern embedded system architectures. Engineered for efficiency, the controller delivers high data throughput while maintaining low power consumption, making it an ideal fit for real-time applications for image processing, edge AI, machine vision, and industrial automation.

The reference design is developed with Lattice Propel™ Builder, a comprehensive suite of graphical and command-line tools designed to accelerate development and simplify system integration. With features like drag-and-drop IP instantiation and flexible configuration options, Propel Builder enables rapid prototyping without compromising design flexibility or performance.

A key component of the design is a RISC-V® processor, offering developers an open, modular, and scalable instruction set architecture. This integration supports a wide range of use cases, from academic research to custom hardware acceleration.

“Our goal with the HyperRAM™ Reference Design was to give developers a powerful, efficient, and easy-to-integrate solution for handling complex memory workloads,” said Andrey Sedachev, Founder of Citrobits. “By combining our high-speed HyperBus™ Controller with the flexibility of Lattice Propel tools and the openness of RISC-V, we’re enabling faster development cycles and empowering innovation across a wide range of embedded vision applications.”

“We’re excited to see Citrobits leverage the performance and power efficiency of our FPGA platforms to bring this innovative reference design to life,” said Kambiz Khalilian, Sr. Director, Ecosystem Partnerships at Lattice Semiconductor. “Solutions like the HyperRAM™ Reference Design demonstrate how our tools and silicon can accelerate development and unlock new possibilities in embedded vision and edge AI.”

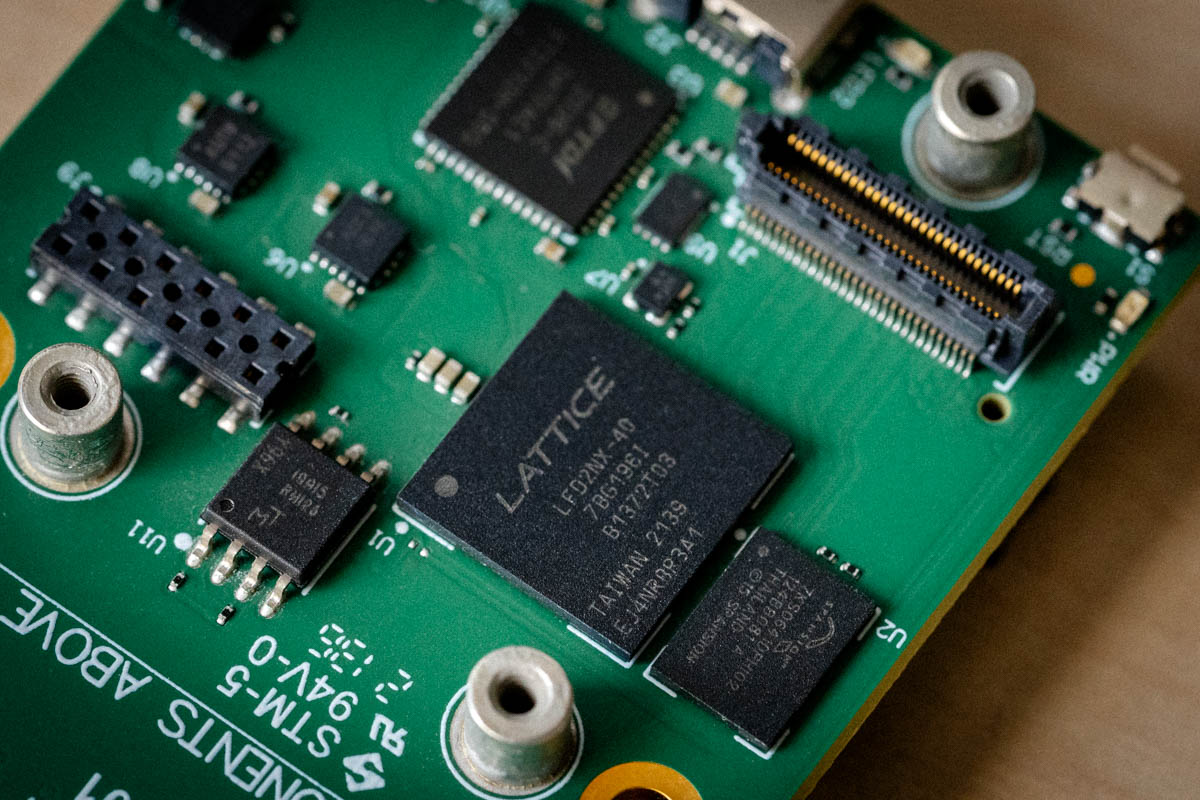

The Citrobits HyperRAM™ Reference Design is available for download as a ZIP archive, which includes the complete reference design and a 30-minute trial version of the IP core. The design is fully compatible with the CR00103 board (PCB revisions 01 to 03), powered by the Lattice Certus™-NX FPGA. The IP core supports multiple Lattice FPGA families, including CrossLink™-NX, CrossLinkU™-NX, Certus™-NX and CertusPro™-NX devices.

Please see below links for more information on the HyperRAM reference design

- Download the HyperRAM reference design here:

- Citrobits HyperRAM IP

- HyperBus Controller

- CRUVI Certus-NX board