RPC® MEMORY CONTROLLER

Overview

This RPC® Memory Controller IP is designed specifically for industrial applications. It is interfaced with the Etron Technology RPC DRAM® Component, and uses Simplified User Interface which supports either 64- or 128-bit data width.

The design is implemented in Verilog HDL. The IP Core can be targeted to CertusPro™-NX FPGA devices. The IP Core is implemented using the Lattice Radiant™ software integrated with the Synplify Pro® synthesis tool.

Features

The key features of Memory Controller Interface IP Core are described below:

- Interfaces with Etron Technology RPC DRAM®

- Provides simplified user interface which supports data width of 64- and 128-bits

- Supports up to 2 Ranks with a capacity of 512 Mb (2 x 256 Mb)

- Currently supports DRAM frequency of 400MHz and a system frequency of 100MHz

- Read/Write burst across 2KB page boundary

- Data Mask Generation

- Burst length support

- 1 – 256 for 64-bit data length

- 1 – 127 for 128-bit data length

- FPGA Device – Lattice CertusPro-NX

Block Diagram

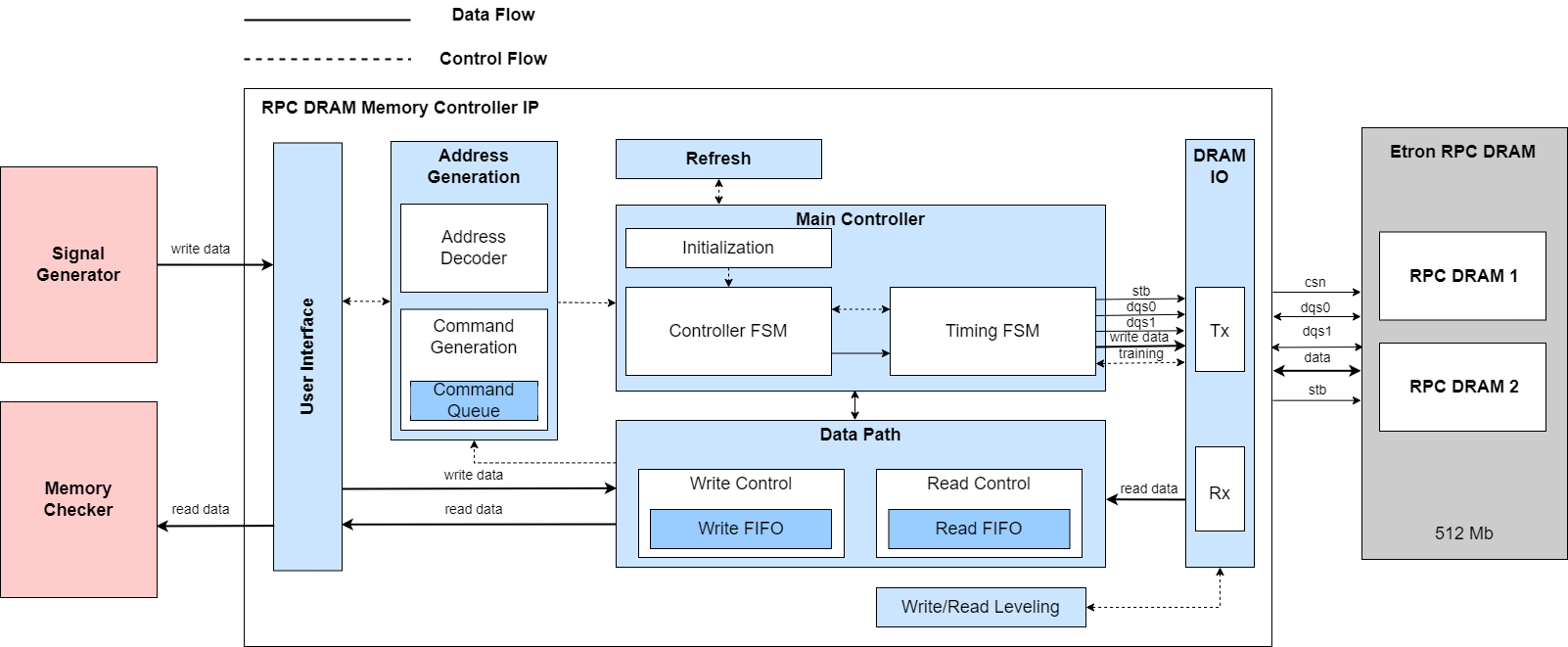

The Memory Controller IP Core consists of five main blocks: Address Generation, Controller FSM, Timing FSM, Data Path and IO Module. Figure 1 provides an overview of how the IP Core is hooked up. The AHB-Lite interface provides access to external memory to issue reads and writes.

The RPC DRAM® Memory Controller IP contains the following functional blocks:

- Reset Module

- Synchronizes the release of asynchronous reset across multiple clock domains.

- User Interface

- This block provides 64-bit and 128-bit simplified user interface on the users side. It currently supports single Read and Write client.

- Address Generation Module

- The Address Generation module is responsible for decoding of the transaction request information from User Interface.

- Data Path Module

- This functional block is responsible for the exchange of data between the User Interface and the RPC DRAM® memory.

- Main Controller

- The Main Controller module is responsible for taking commands from the command queue and issuing them with proper DRAM signals to RPC DRAM® with all the timing parameters maintained.

- Refresh Module

- This module is responsible for periodic refresh of the RPC DRAM® memory.

- IO Module

- I/O module acts as the interface between RPC DRAM® Controller and the RPC DRAM® memory module.

Applications

RPC® memory finds widespread application in video processing, it serves as a buffer memory for storing intermediate results during video encoding and decoding processes, thereby facilitating efficient data transfer and manipulation.

Its low pin count configuration makes it ideal for integration into system-on-chip (SoC) designs, reducing the complexity of interconnections. RPC® memory also functions as a frame buffer, holding video frames for real-time processing tasks like filtering, scaling, and motion estimation.

In video surveillance systems, RPC® memory aids in storing and processing large volumes of video data, enabling quick retrieval and analysis for security purposes. Additionally, it is utilized in multimedia devices such as set-top boxes and smart TVs to store and stream high-definition content seamlessly.

Trusted Suppliers

Located in Taiwan and serving the international marketplace across the US, Europe, Asia, and Japan, Etron Technology Inc. is a company specialized in system-on-chips, logic chip designs, electronic applications, and DRAM products, including the high-bandwidth and low pincount RPC DRAM®, which is a pioneer in the field of memory technology.

Thanks to its innovative solutions, Etron Technology has been several times recognized with the CES Innovation Award at the Consumer Electronics Show.

Etron Technology is a trusted supplier for Citrobits, offering sustainable, compact, and powerful components for the most demanding solutions. This strategic alliance combines Etron’s expertise in component manufacturing with Citrobits’ innovative spirit, resulting in the development of products that meet the highest standards of quality and efficiency.